Lecture notes in computer science, vol 2523. Cryptographic Hardware and Embedded Systems – CHES 2002. Klimov A, Shamir A (2003) A new class of invertible mappings. With N bits a Maximal LFSR will have (2N) - 1 states. When considering the implementation of the LFSR, the bit width of the random number and the repeatability of the number need to be considered.

Lecture notes in computer science, vol 4859. Implementation is relatively simple, a shift register with a number of terms XORd together to create the feedback term. Sekar G, Paul S, Preneel B (2007) Related-key attacks on the Py-family of ciphers and an approach to repair the weaknesses. SASC: the State of the Art of Stream Ciphers, NoE ECRYPT Workshop Technical Report, University of Waterloo, CORR 2000–20įiliol E, Fontaine C, Josse S (2004) The COSvd ciphers. Youssef AM, Gong G (2000) On the quadratic span of binary sequences. Lecture notes in computer science, vol 435. Jansen CJA, Boekee DE (1990) The shortest feedback shift register that can generate a given sequence. Jansen CJA (1989) Investigations on nonlinear stream cipher systems: construction and evaluation methods. The work is supported, and formulated using very high speed integrated circuit hardware description language (VHDL) programming in Xilinx ISE 14.7 software.Golomb SW (1982) Shift register sequences, revised edition. The concept of this design is programmable and can be extended to n-bit based on the applications. The novelty of the work is that the design is scalable and can be extended based on the requirements of the systems which is synthesized and experimentally verified on the Zynq-7000 field programmable gate array (FPGA) board. The article proposes the hardware chip design and simulation of two 5-bit LFSR modules used for the gold sequence generator applicable for the communication systems.

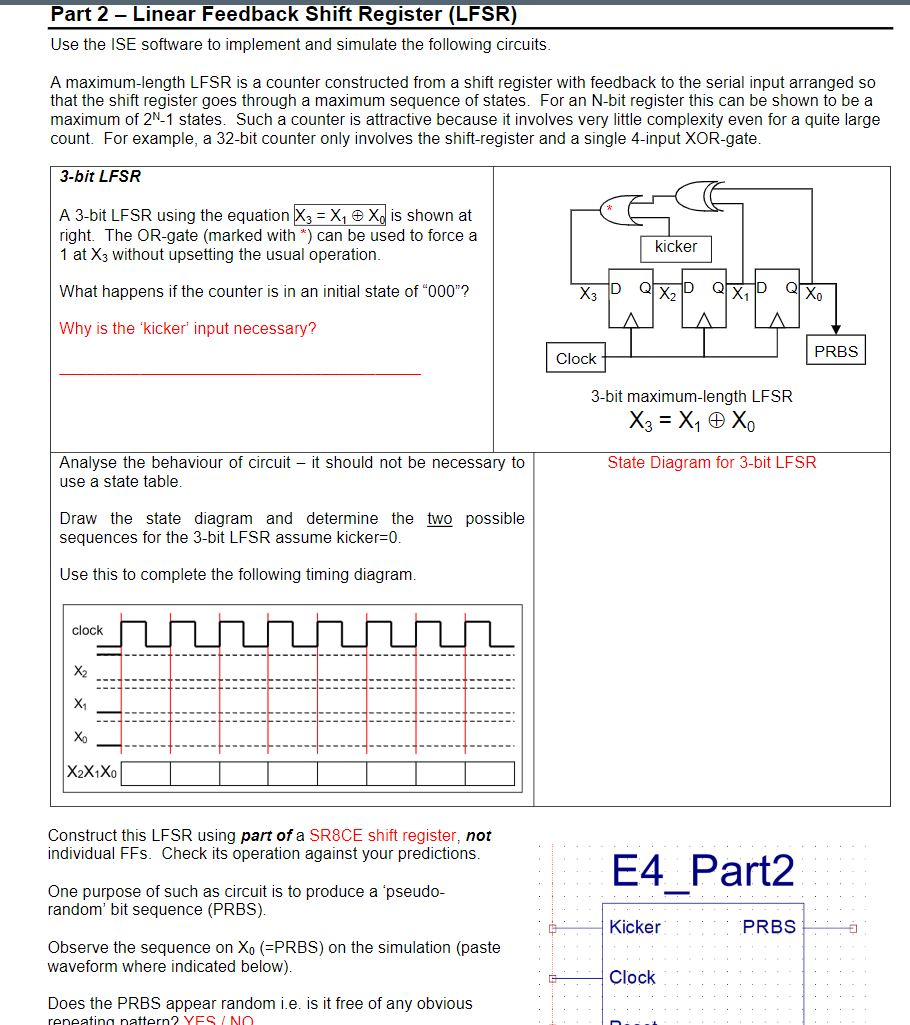

The motivation of the work is to generate the Gold code sequence by the integration of two LFSR. The hardware chip design and performance estimation of the LFSR is the problem for specific communication system. The LFSR is used in chip hardware for high-speed operations, error control, and the generation of pseudo-random numbers. There are simple shift register-based n-bit counters with a few XOR gates that behave pseudo-randomly. Linear feedback shift register (LFSR) is the basic building block of the communication system used in different coding, error detection and correction codes, such as gold, low-density parity check (LDPC), polar, and turbo codes.

0 kommentar(er)

0 kommentar(er)